# Reference Hardware Design Guideline Control (+SoC) Board

| Version | Date         |

|---------|--------------|

| 1.0     | May 25, 2020 |

|         |              |

|         |              |

|         |              |

|         |              |

|         |              |

|         |              |

|         |              |

|         |              |

|         |              |

|         |              |

|         |              |

|         |              |

|         |              |

## **Panasonic Corporation**

Automotive Company R&D Division

## **Revision History**

| Date         | Version | Comments        |  |

|--------------|---------|-----------------|--|

| May 25, 2020 | 1.0     | Initial Release |  |

|              |         |                 |  |

|              |         |                 |  |

|              |         |                 |  |

|              |         |                 |  |

|              |         |                 |  |

|              |         |                 |  |

## References

| No. | Document                            | Version | Release Date |

|-----|-------------------------------------|---------|--------------|

| 1   | RH_Design_Vehicle_Audio_ver.1.0.pdf | 1.0     | May 25, 2020 |

| 2   | RH_Design_VideoOut_ver.1.0.pdf      | 1.0     | May 25, 2020 |

| 3   | RH_Design_VideoIn_ver.1.0.pdf       | 1.0     | May 25, 2020 |

| 4   | RH_Design_USB_ ver.1.0.pdf          | 1.0     | May 25, 2020 |

| 5   | RH_Design_Ether_ ver.1.0.pdf        | 1.0     | May 25, 2020 |

| 6   | RH_Design_GNSS_ ver.1.0.pdf         | 1.0     | May 25, 2020 |

|     |                                     |         |              |

|     |                                     |         |              |

|     |                                     |         |              |

|     |                                     |         |              |

|     |                                     |         |              |

## Contents

| 1. | Overview                                     | 6 |

|----|----------------------------------------------|---|

| 2. | Hardware Structure                           | 6 |

| 2  | 2.1. Outline and Composition                 | 8 |

| 3. | Vehicle/Audio Board Outline                  |   |

| 4. | Control Board Outline                        |   |

| 5. | Power Supply Configuration                   |   |

| Ę  | 5.1. Control Board Power Supply              |   |

| 6. | Block-to-Block Signals                       |   |

| e  | 6.1. Connector                               |   |

| e  | 6.2. Connector Pin Assignment                |   |

|    | 6.3. Signal Level Consistency                |   |

| 7. |                                              |   |

| 7  | 7.1. Block Diagram                           |   |

| 7  | 7.2. Power Supply Configuration              |   |

| 7  | 7.3. Power Sequence                          |   |

| 7  | 7.4. Circuit Structure                       |   |

| 7  | 7.5. Block-to-Block Connector Pin Assignment |   |

| 8. | Disclaimer                                   |   |

## **Figures and Tables**

| Figure 1 Reference Hardware Board Structure                                           | 6  |

|---------------------------------------------------------------------------------------|----|

| Figure 2 Overall Connection                                                           | 7  |

| Figure 3 Assembled Hardware Structure                                                 | 8  |

| Figure 4 Control Board Structure                                                      | 9  |

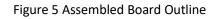

| Figure 5 Assembled Board Outline                                                      |    |

| Figure 6 Board position viewed from back side of enclosure                            |    |

| Figure 7 Board position view from the top side of enclosure                           | 11 |

| Figure 8 Vehicle/Audio Board Outline                                                  |    |

| Figure 9 Vehicle/Audio Board Component Height Constraint                              |    |

| Figure 10 Control Board Outline                                                       |    |

| Figure 11 Control Board Component Height Constraint                                   |    |

| Figure 12 Power Supply Diagram                                                        |    |

| Figure 13 Control Board Power Supply Schematic                                        |    |

| Figure 14 120-pin Board-to-Board Connector                                            |    |

| Figure 15 Block-to-Block Connector Matching Part Numbers                              |    |

| Figure 16 Block-to-Block Connector Features                                           | 21 |

| Figure 17 Block-to-Block Connector Pin Application                                    | 21 |

| Figure 18 Block-to-Block Connector Consideration                                      |    |

| Figure 19 Block-to-Block Connector Signal Type Grouping                               |    |

| Figure 20 Board-to-Board Signal Voltage Level Compatibility of Signals between Boards |    |

| Figure 21 R-Car H3 Reference Hardware Structure                                       |    |

| Figure 22 R-Car H3 Reference Hardware External Interfaces                             |    |

| Figure 23 Block Diagram                                                               |    |

| Figure 24 Power Supply Schematic                                                      |    |

| Figure 25 Power ON Sequence                                                           |    |

| Figure 26 Control (+SoC) Board Schematic                                              |    |

| Table 1 Control Board Power Supply Current Rating                                     |    |

| Table 2 Block-to-Block Connector Specifications                                       |    |

| Table 3 Functional Specifications                                                     |    |

#### 1. Overview

This document includes principles and steps for circuits and boards design of Reference Hardware.

Reference Hardware aims to provide a standard environment for developing in-vehicle infotainment system and so on. Reference Hardware consists of PCBs with a different functionality. Therefore, a SoC or peripheral circuitry can be easily replaced without compatibility issues when a common principal design is adopted. It helps build development environment faster and is able to be directly installed in a vehicle when the size is 2DIN.

#### 2. Hardware Structure

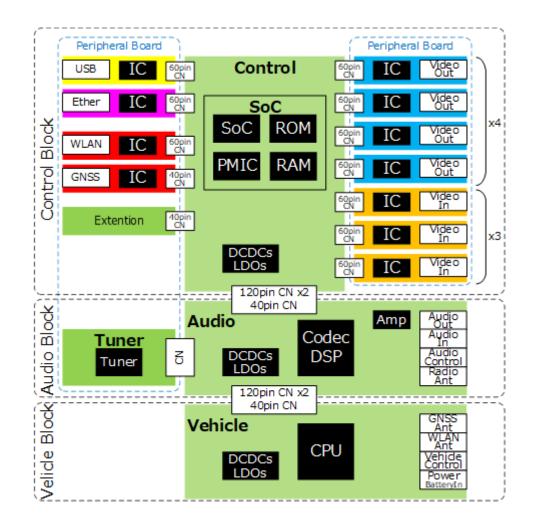

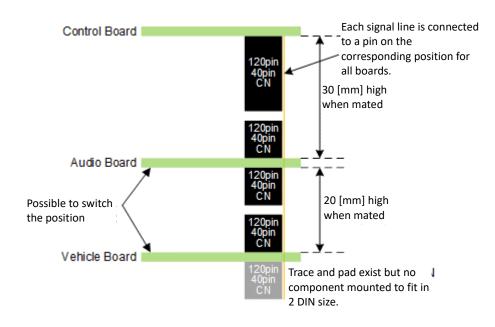

The structure consists of three main blocks: Vehicle block which processes vehicle signals and in-vehicle networks such as CAN, Audio block which processes sound input and output, and Control block which processes MultiMedia and HLOS, etc. Boards are grouped into each block and the same two 120pin connector and one 40pin connector are used to connect between blocks. Same signals are connected in the same manner. Vehicle block and Audio block can be combined as one block depending on a scale or purpose of the development.

Each peripheral circuit, or peripheral board, is divided by one specific functionality which enables various configuration to meet different purposes or functional requirements.

Figure 1 shows overall board structure.

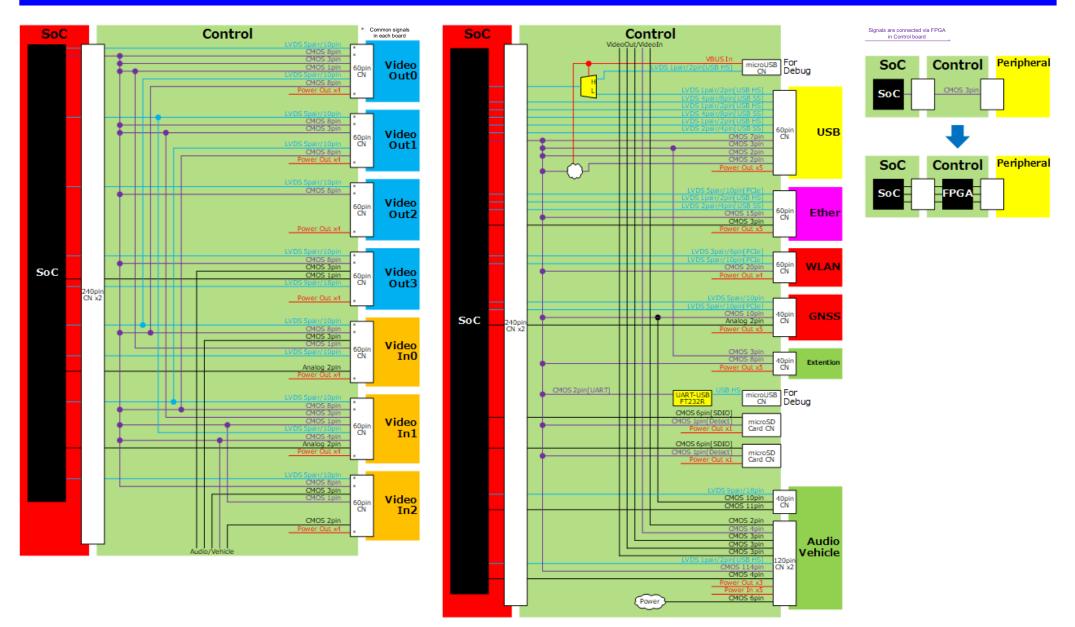

Figure 2 shows that the control signals are transmitted between the SoC and each peripheral board via FPGA on Control Board, and the connecting terminals can be changed by reconfiguring the FPGA's internal circuit.

Figure 1 Reference Hardware Board Structure

## Reference Hardware Design Guideline for Control (+SoC) Board

Figure 2 Overall Connection

## 2.1. Outline and Composition

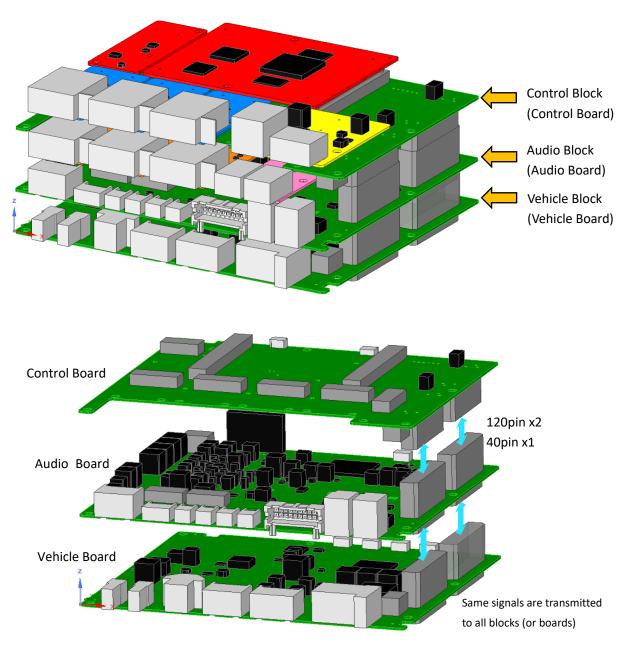

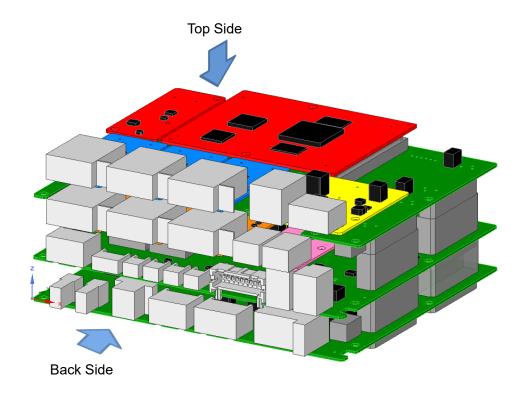

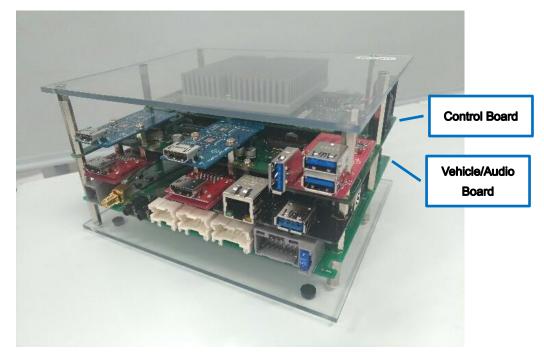

Figure 3 Assembled Hardware Structure

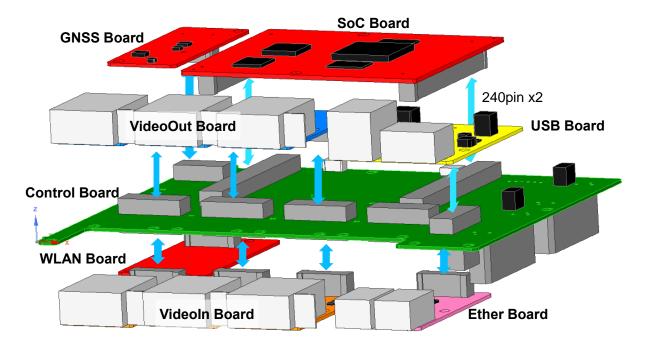

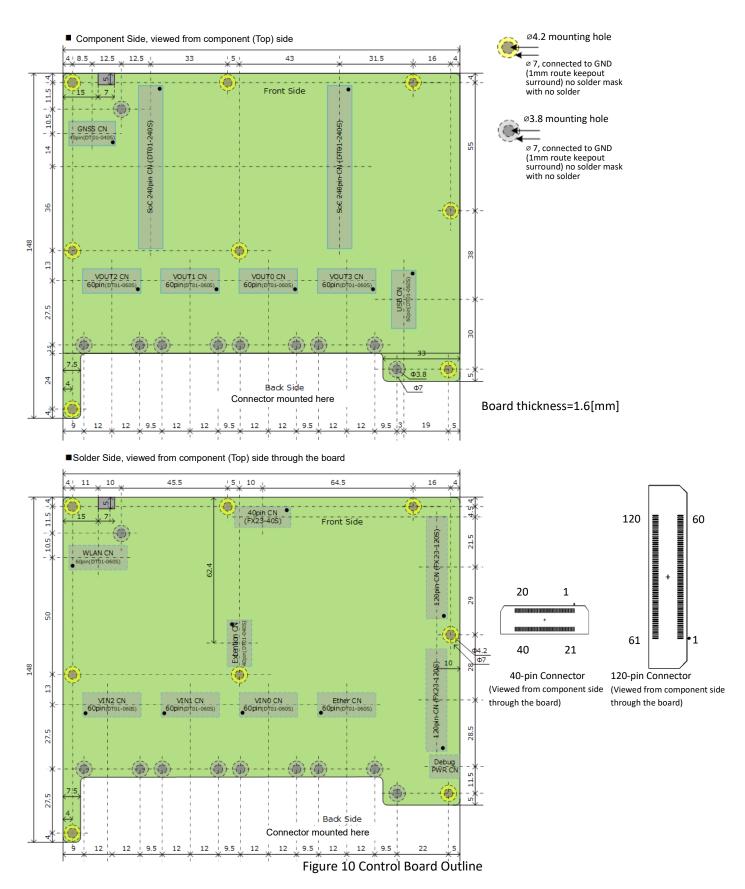

Boards with different functionality including SoC can be connected to Control Board. Each Peripheral Board provides a distinctive functionality and that is SoC Board, GNSS Board, WLAN Board, VideoOut Board x4, VideoIn Board x3, USB Board, Ether Board, or Extension Board.

SoC Board is connected by two 240pin board-to-board connectors, GNSS Board and Extension Board are connected by 40pin board-to-board connector, WLAN Board, VideoOut Board, VideoIn Board, USB Board, Ether Board are connected by 60-pin board-to-board connector.

Figure 4 Control Board Structure

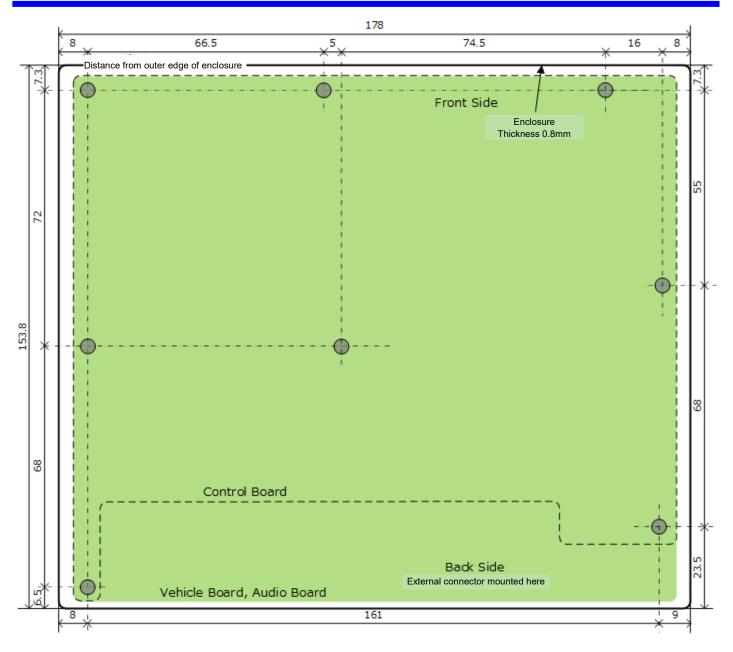

Figure 6 Board position viewed from back side of enclosure

Figure 7 Board position view from the top side of enclosure

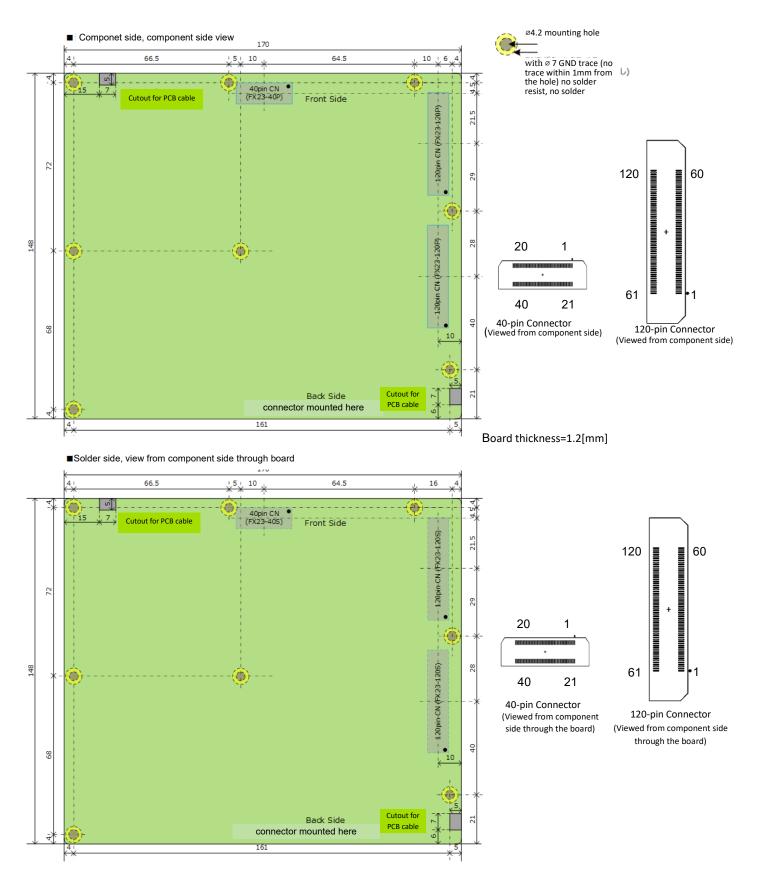

#### 3. Vehicle/Audio Board Outline

Figure 8 Vehicle/Audio Board Outline

- 0  $(\mathbf{\hat{O}})$  $(\bigcirc)$ 40pin CN (FX23-40P) 120pin CN (FX23-120P) /• Component (Bottom) Side Max Component Height: 12.5mm (Ĉ 122 (Except for connectors shown here) 120pin CN (FX23-120P)  $\odot$  $\bigcirc$ 6 Ô 26 Max Component Height: 16 mm 1 0

- Componet side, component side view

■ Solder side, view from component side through the board

Figure 9 Vehicle/Audio Board Component Height Constraint

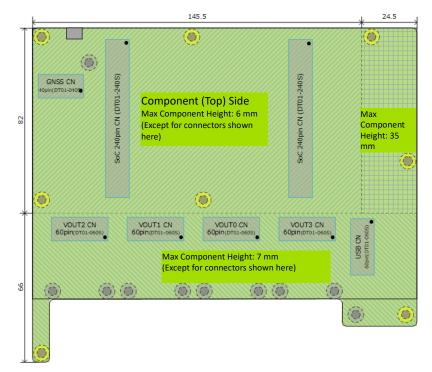

#### 4. Control Board Outline

Component side, vied from component (Top) side

■ Solder side, viewed from component side through the board

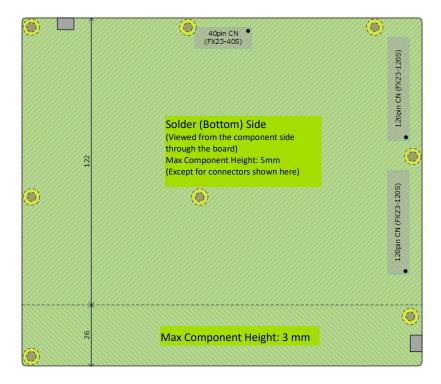

Figure 11 Control Board Component Height Constraint

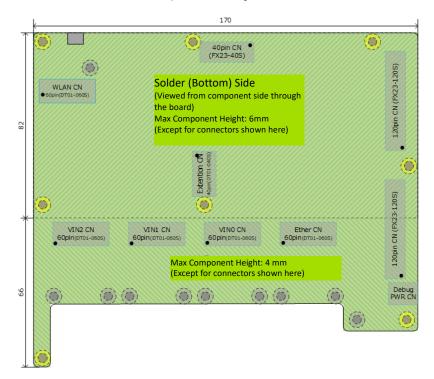

#### 5. Power Supply Configuration

Power from vehicle battery (+12[V]) is supplied to Vehicle Board. +12[V] is distributed to each board via Vehicle Board. Power each board requires should be generated within the boards from+12[V] basically. +5.8[V] and +3.8[V] power supplies are built on Vehicle Board are connected along with +12[V] through a 120pin connector. +5.8[V] is used for the source of commonly used +5[V] power supply and +3.8[V] is used for the source of commonly used +3.3[V] and +1.8[V] power supplies. When current from +12[V] power used on each board is not enough, +12[V] can be supplied via other dedicated connector (BATT connector) instead of 120pin connector. Components supplied +12[V] from vehicle should use withstand voltage higher than +27[V]. Power IC should be designed to be non-flammable or smoke-free when shorted at output side. Use of Power IC with OCP (Over Current Protection) is recommended.

Total of 11[A] is the current capacity of the 120pin connector can provide at +12[V] through 10 pins rated for 0.5[A/pin] and 2 pins rated for 3.0[A/pin]. Current rating which +12[V] from BATT connector can supplies is 9[A] when a cable used is higher than AWG28 (bigger than AWG28) as 6 pins of 1.5[A/pin] is used.

DCDC/inductor's capacity for the source of +5V power supply line is 5.5[A], and the current capacity of 11 pins rated for 0.5[A/pin] is 5.5[A]. DCDC/inductor's capacity for the source of +3.3V power supply line is 3.5[A], and the current capacity of 7 pins rated for 0.5[A/pin] is 3.5[A]. However, as both power supplies are used in Vehicle Board (0.5[A] retained), 5.0[A] from the source of +5V power supply and 3.0[A] from the source of +3.3V power supply are the electrical current can be consumed on Audio Board and Control Board.

Power that terminals require for signaling between boards is also supplied via the120pin connector.

Vehicle board supplies power to the terminals required for the board through the signal named as IO\_VEHICLE, Audio board supplies power to its terminals through the signal named as IO\_AUDIO, and Control boards suppliers power to its terminals through the signals named as IO\_PF (for SoC terminals), IO\_VIDEO (for VideoOut board terminals) and IO\_IF (USB board terminals)

Figure 12 Power Supply Diagram

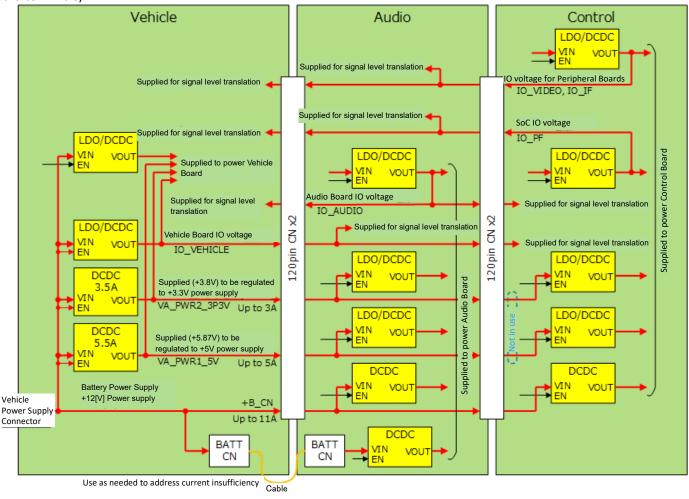

#### 5.1. Control Board Power Supply

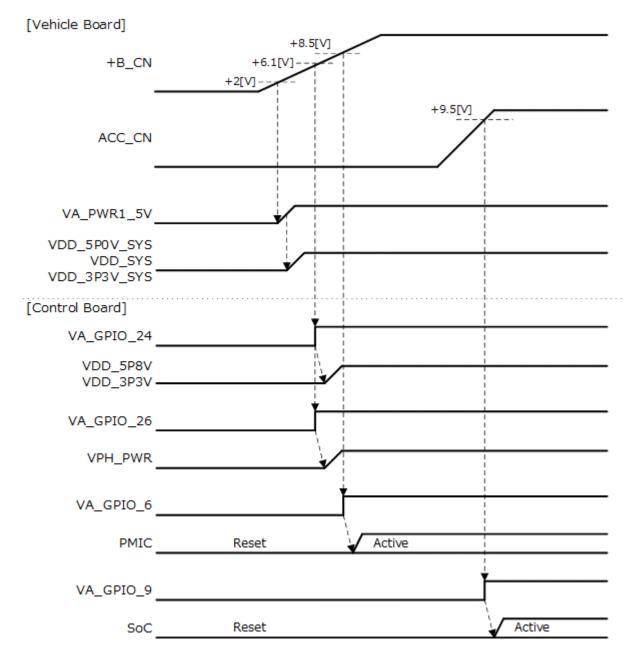

Power supply circuit for Control Board is shown in Figure 13. VDD 5P8V voltage and VDD 3P3V voltage, Control Board's main power supplies, are controlled by VA GPIO 24 (H is ON), from Vehicle board. VPH PWR voltage, or SoC's main power supply, is controlled by VA GPIO 26 (H is ON) from Vehicle board.

Figure 13 Control Board Power Supply Schematic

#### Reference Hardware Design Guideline for Control (+SoC) Board

Table 1 shows current rating of each power supply and assigned amperage of power consumed at the destination terminal. If the assigned amperage for the destination terminal is not sufficient, it can be adjusted according to the consumption in other boards. (If there's power that is not consumed in another board and is usable, it can be added to where more power is required.) See design specification of each board.

| Valtaga Nama    | Input Valtaga*1             | Quiteut Valtaga | Current | urrent Power Supply Destination and Assigned Current Capacity |          |                       |        |        |       |          |         |        |       |

|-----------------|-----------------------------|-----------------|---------|---------------------------------------------------------------|----------|-----------------------|--------|--------|-------|----------|---------|--------|-------|

| Voltage Name    | Input Voltage <sup>*1</sup> | Output Voltage  | Rating  | Total                                                         | Subtotal | Control <sup>*2</sup> | SoC    | WLAN   | GNSS  | VOUT(x4) | VIN(x3) | USB    | Ether |

| VPH_PWR         | +B_VPH                      | 3.4-5V          | 11.0A   | 6.6A                                                          | 4.8A     |                       | 4800mA |        |       |          |         |        |       |

| VPH_PWR_WLAN    | VPH_PWR                     | VPH_PWR         | 2.0A    | -                                                             | 1.2A     |                       |        | 1200mA |       |          |         |        |       |

| VPH_PWR_GNSS    | VPH_PWR                     | VPH_PWR         | 2.0A    | -                                                             | 0.8A     |                       |        |        | 800mA |          |         |        |       |

| VDD_5P8V        | +B_CN                       | 5.87V           | 3.0A    | 3.0A                                                          | 2.95A    |                       |        | 200mA  | 150mA | 200mA    | 200mA   | 1000mA | 200mA |

| VCCAUX_FPGA     | VDD_5P8V                    | 3.3V            | 0.2A    | -                                                             | 0.05A    | 50mA                  |        |        |       |          |         |        |       |

| VDD_3P3V        | +B_VPH                      | 3.3V            | 5.5A    | 5.5A                                                          | 1.9A     | 100mA                 |        |        |       | 200mA    | 200mA   | 200mA  | 200mA |

| VDD_1P8V        | VDD_3P3V                    | 1.8V            | 1.0A    | 1.0A                                                          | 0.8A     |                       |        |        |       |          | 200mA   |        | 200mA |

| VDD_1P8V_VO     | VDD_3P3V                    | 1.8V            | 1.0A    | -                                                             | 0.8A     |                       |        |        |       | 200mA    |         |        |       |

| VCC_FPGA        | VDD_3P3V                    | 1.2V            | 1.0A    | -                                                             | 0.1A     | 100mA                 |        |        |       |          |         |        |       |

| VDD_ADJ         | VDD_3P3V                    | 1.2V            | 1.0A    | 0.4A                                                          | 0.0A     |                       |        |        |       |          |         |        |       |

| VDD_ADJ2        | VDD_3P3V                    | 1.5V            | 1.0A    | 1.0A                                                          | 0.0A     |                       |        |        |       |          |         |        |       |

| VDD_WLAN_IO     | VREG_SOC_IO                 | 3.3V            | 0.2A    | -                                                             | 0.1A     |                       |        | 100mA  |       |          |         |        |       |

| VDD_GNSS_IO     | VREG_GNSS_IO                | 3.3V            | 0.2A    | -                                                             | 0.1A     |                       |        |        | 100mA |          |         |        |       |

| VDD_VOUT_IOBANK | VDD_3P3V                    | 3.3V            | 0.2A    | -                                                             | 0.1A     | 100mA                 |        |        |       |          |         |        |       |

| VDD_VIN_IOBANK  | VDD_3P3V                    | 3.3V            | 0.2A    | -                                                             | 0.1A     | 100mA                 |        |        |       |          |         |        |       |

| VDD_USB_IOBANK  | VDD_3P3V                    | 3.3V            | 0.2A    | -                                                             | 0.1A     | 100mA                 |        |        |       |          |         |        |       |

| VDD_VOUT_CORE   | VDD_ADJ2                    | 1.5V            | 1.0A    | -                                                             | 0.6A     |                       |        |        |       | 150mA    |         |        |       |

| VDD_VIN_CORE    | VDD_ADJ2                    | 1.5V            | 1.0A    | -                                                             | 0.3A     |                       |        |        |       |          | 100mA   |        |       |

| VDD_ETH_CORE    | VDD_ADJ                     | 1.2V            | 1.0A    | -                                                             | 0.2A     |                       |        |        |       |          |         |        | 200mA |

| VDD_GNSS_CORE   | VDD_ADJ2                    | 1.5V            | 1.0A    | -                                                             | 0.1A     |                       |        |        | 100mA |          |         |        |       |

| VDD_USB_1P8V    | VDD_1P8V                    | 1.8V            | 1.0A    | -                                                             | 0.2A     |                       |        |        |       |          |         | 200mA  |       |

| VDD_USB_CORE    | VDD_ADJ                     | 1.2V            | 1.0A    | -                                                             | 0.2A     |                       |        |        |       |          |         | 200mA  |       |

Table 1 Control Board Power Supply Current Rating

Settings in this table are defaults (preselected when released initially) and can be adjusted.

#### 6. Block-to-Block Signals

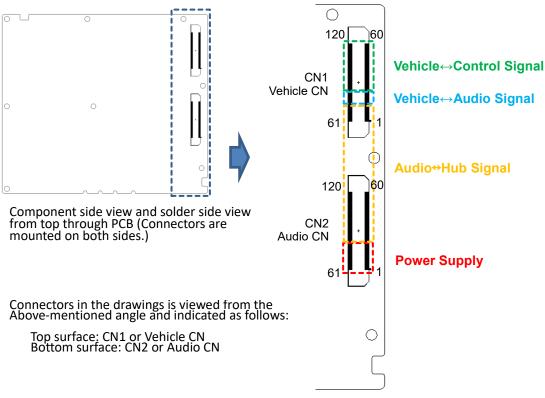

Vehicle Board, Audio Board, and Control Board each use two 120pin Board-to-Board connectors and one 40pin Board-to-Board connector.

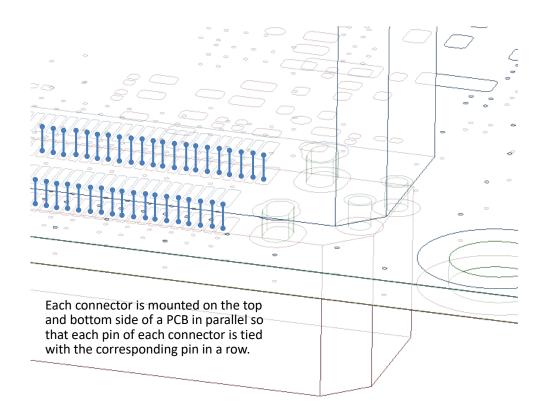

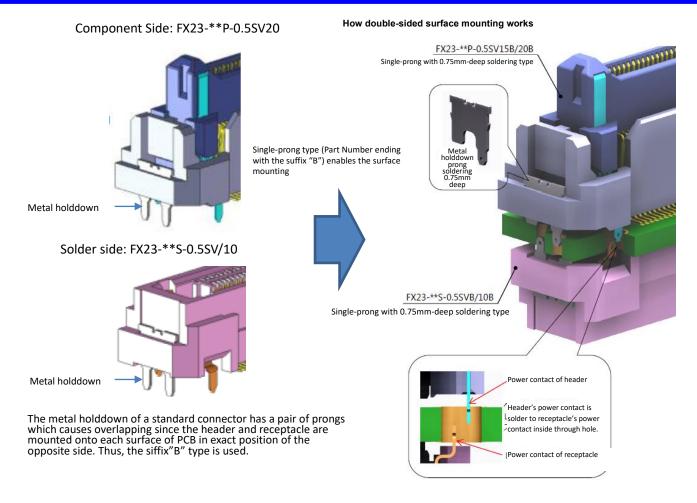

120pin/40pin connectors are mounted on both component side and solder side of Vehicle Board or Audio Board and each pin of the boards are vertically connected.

120pin/40pin connectors of Vehicle Board, Audio Board, and Control Board should be mounted in the positions where the pins on each board can exactly match to transmit the same signal between the boards. The signals of terminals except the terminals decided signals such as power supply, etc., can be used for optional signals between the boards. It is optional but recommended to use preconfigured pin assignments as the pins are configured with the intention to meet expected application purposes.

Figure 14 120-pin Board-to-Board Connector

#### 6.1. Connector

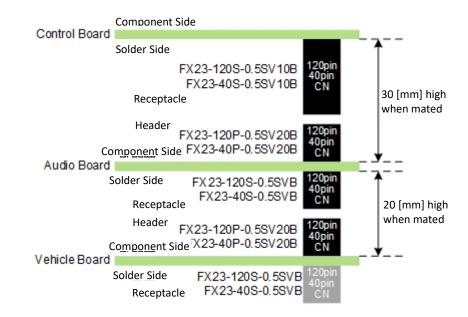

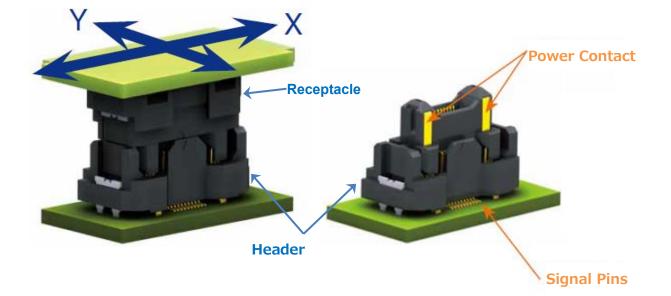

Two 120pin Board-to-Board connectors and one 40pin Board-to-Board connector are used to connect Control Board, Vehicle Board and Audio Board. These three connectors are referred to as "block-to-block connector" in this document.

FX23 series of Hirose Electric Co., Ltd. is used for the block-to-block connector. The floating structure (±0.6 [mm] in X and Y directions) type is used to mitigate position gap and oscillation effect.

FX23-120P-0.5SV20B and FX23-40P-0.5SV20B on component side, FX23-120S-0.5SVB and FX23-40S-0.5SVB (FX23-120S-0.5SV10B and FX23-40S-0.5SV10B are used to keep a 30mm stack height for the Control Board.) on solder side are used. A PCB with each connector should be arranged on top and bottom surface of the same axis with parallel connecting. (Same signals are assigned to all the terminals of 120pin/40pin connectors on Control board, Vehicle board, and Audio board)

|                          | FX23 Series                      |                                                                                    |  |  |  |  |

|--------------------------|----------------------------------|------------------------------------------------------------------------------------|--|--|--|--|

|                          | Signal                           | Power Supply Part<br>(There are 4 terminals in addition to<br>the ones for signal) |  |  |  |  |

| Current Rating (per pin) | FX23 Series                      | FX23 Series                                                                        |  |  |  |  |

| Withstand Voltage        | Signal Signal                    |                                                                                    |  |  |  |  |

| Contact Resistance       | 0.5[A] 0.5[A]                    |                                                                                    |  |  |  |  |

| Insulation Resistance    | AC150[V], 1 min AC150[V], 1 min  |                                                                                    |  |  |  |  |

| Operating Temp:          | -55 up to +105[°C]               |                                                                                    |  |  |  |  |

| Floating Range           | ±0.6[mm] in X and Y directions   |                                                                                    |  |  |  |  |

| Applicable Signal        | 8+[Gbps],<br>Differential 100[Ω] |                                                                                    |  |  |  |  |

Table 2 Block-to-Block Connector Specifications

Figure 15 Block-to-Block Connector Matching Part Numbers

Figure 16 Block-to-Block Connector Features

Figure 17 Block-to-Block Connector Pin Application

Figure 18 Block-to-Block Connector Consideration

Figure 19 Block-to-Block Connector Signal Type Grouping

#### 6.2. Connector Pin Assignment

To find the information about pin assignment of each connector, please refer to respective design guidelines.

#### 6.3. Signal Level Consistency

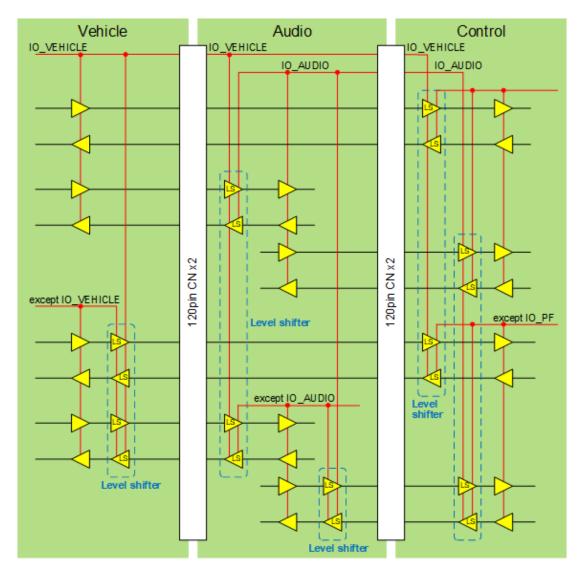

Figure 20 illustrates points to note on voltage levels to manage signals between Control, Audio, and Vehicle Boards.

The voltage levels of signals transmitted from/to Audio board, Control board, CN1 and CN2 on Vehicle Board do not require special care. However, voltage level of pins for input and output signal for Vehicle Board except for the pin to supply power for the signal pins, or IO\_VEHICLE, should be shifted to the level of IO\_VEHICLE voltage Signals transmitted via CN3 are directly connected to SoC so that the voltage level may need to be regulated on Vehicle Board according to the SoC specification.

Signals transmitted between Control Board, CN1 and CN2 on Audio Board do not have voltage level requirement. However, voltage levels of input and output signals, which is not the level of IO\_AUDIO voltage for input and output signals of Audio Board, should be shifted to the level of IO\_AUDIO voltage.

The voltage level of signals transmitted via Vehicle Board, CN1 and CN2 should be shifted to the level of IO\_VEHICLE power supply voltage.

On Control Board, the voltage level of signals transmitted between Vehicle Board and Control Board via CN1 and CN2 should be shifted to IO\_VEHICLE voltage level, the voltage level of signals transmitted between Audio Board and Control Board as well shoud be shifted to IO\_AUDIO voltage level. Each signal voltage level is listed on the table of Connecter Pinout in design guidelines of each functional board.

Figure 20 Board-to-Board Signal Voltage Level Compatibility of Signals between Boards

## 7. R-Car H3 Reference Hardware Structure and Specifications

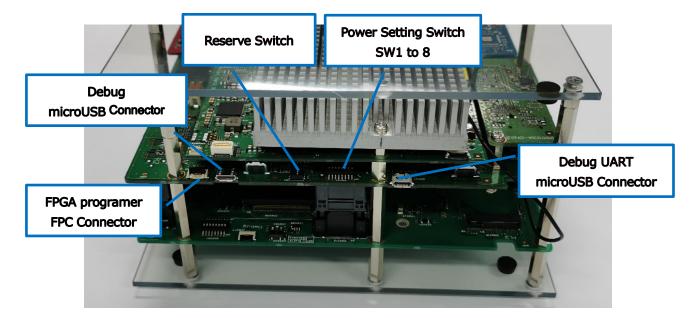

In R-Car H3 Reference Hardware, Vehicle Board and Audio Board are combined as one board.

Figure 21 R-Car H3 Reference Hardware Structure

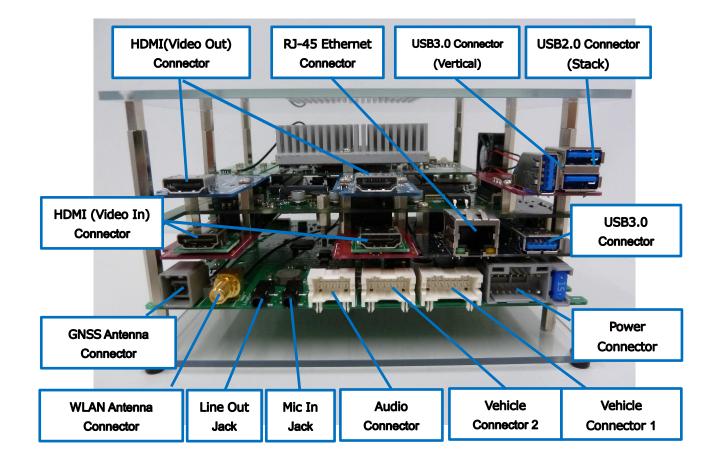

Figure 22 R-Car H3 Reference Hardware External Interfaces

Functional specifications supported by R-Car H3 Reference Hardware are listed on Table 3.

#### Table 3 Functional Specifications

| Block                 | Spec.                                                        |  |  |  |

|-----------------------|--------------------------------------------------------------|--|--|--|

| CPU                   | R-CAR H3 SiP                                                 |  |  |  |

| Memories              | • 8GByte LPDDR4                                              |  |  |  |

|                       | • 16MByte QSPI FlashROM                                      |  |  |  |

|                       | • 64GByte eMMC                                               |  |  |  |

| Connectors            | External Connectors x 4 (Power, GPIO, CAN, etc.)             |  |  |  |

|                       | WLAN antenna/GPS antenna                                     |  |  |  |

|                       | Line Out Jack/Mic In Jack                                    |  |  |  |

|                       | Debug USB/Debug UART                                         |  |  |  |

|                       | MicroSD Card Socket                                          |  |  |  |

|                       | • USB3.0 x 2 / USB2.0 x 2                                    |  |  |  |

|                       | RJ-45 Ethernet(1000Base-T)                                   |  |  |  |

|                       | HDMI(Video Out) x 2/HDMI(Video In) x 2                       |  |  |  |

| Board configuration   | SoC Board                                                    |  |  |  |

|                       | Control Board                                                |  |  |  |

|                       | Vehicle Board                                                |  |  |  |

|                       | VideoOut Board x 2                                           |  |  |  |

|                       | • VideoIn Board x 2                                          |  |  |  |

|                       | • USB Board                                                  |  |  |  |

|                       | Ether Borad                                                  |  |  |  |

|                       | GNSS Board                                                   |  |  |  |

|                       | (• WLAN Board)                                               |  |  |  |

| Product specification | Dimensions: 154mm x 178mm x 101mm (Excluding protrusions)    |  |  |  |

|                       | • Weight : 1000g                                             |  |  |  |

|                       | External Power supply DC=10.5V~16V@Max 10A                   |  |  |  |

|                       | <ul> <li>Operating ambient temperature -10°C~60°C</li> </ul> |  |  |  |

| Accessories           | AC Adaptor                                                   |  |  |  |

|                       | Power Harness (DC-Jack to External Connector)                |  |  |  |

|                       | External Connector Harness (Reserved)                        |  |  |  |

|                       | GNSS Antenna                                                 |  |  |  |

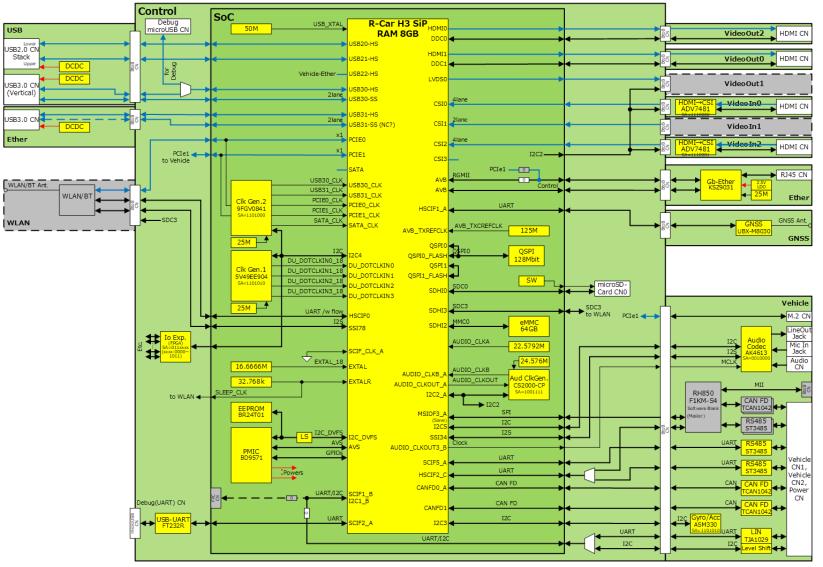

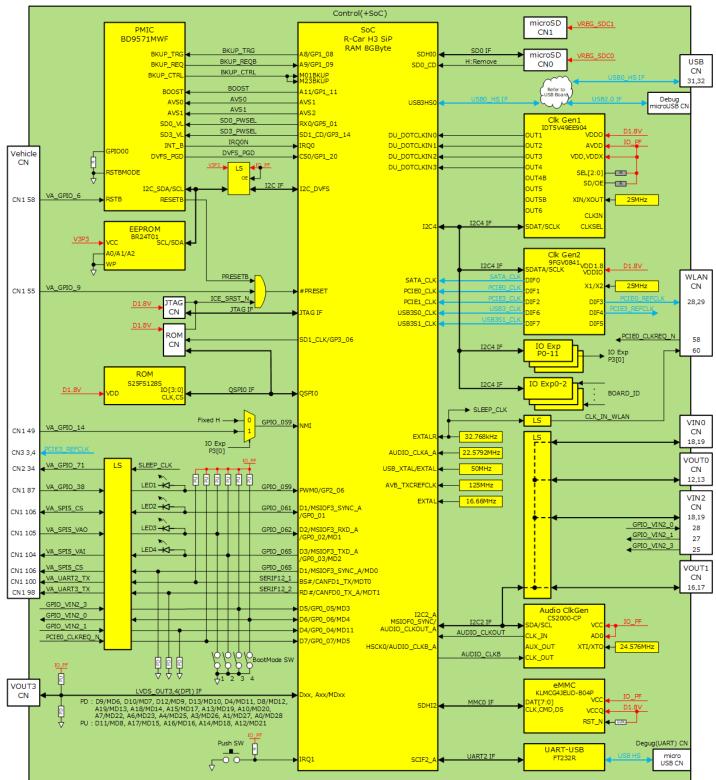

## 7.1. Block Diagram

R-Car H3 Reference Hardware Block Diagram is shown below.

Figure 23 Block Diagram

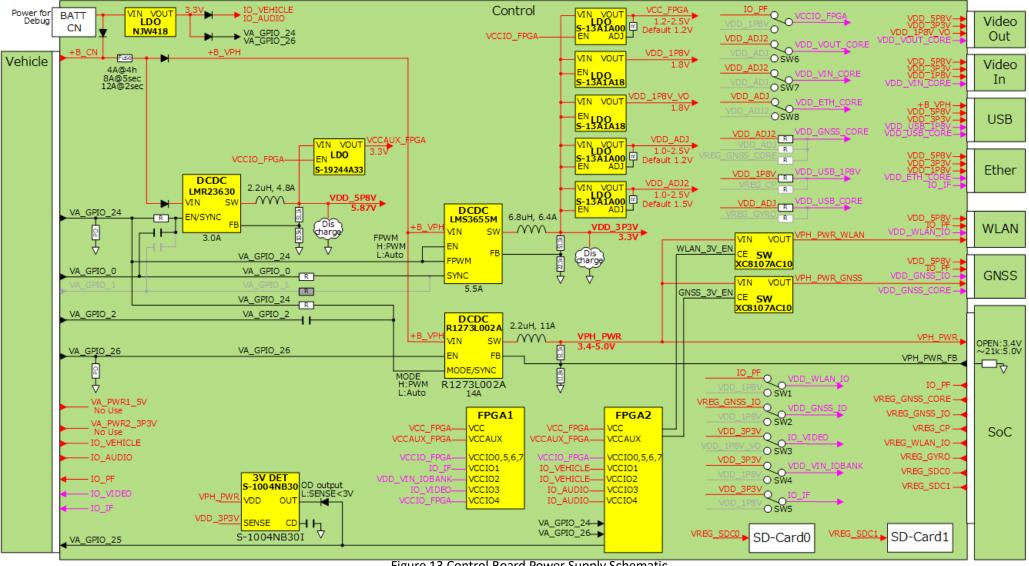

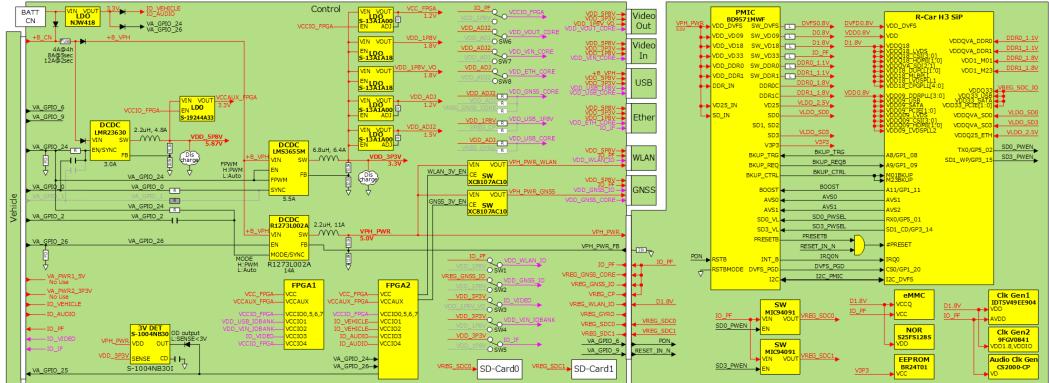

#### 7.2. Power Supply Configuration

The following figure shows power supply circuity of R-Car H3 Reference Hardware Control (+SoC) Board.

Figure 24 Power Supply Schematic

#### 7.3. Power Sequence

Figure 25 shows power ON sequence when Vehicle Board's SoC boot control setting switch (SW 7) is OFF (Hardware Control)

Figure 25 Power ON Sequence

#### 7.4. Circuit Structure

The following figure shows the arrangement and connections between the components in R-Car H3 Reference Hardware Control (+SoC) Board.

Figure 26 Control (+SoC) Board Schematic

### 7.5. Block-to-Block Connector Pin Assignment

To find the information about pin assignment of each connector, please refer to respective design guidelines.

#### 8. Disclaimer

- 1. This document is provided only as a reference material to property use the AGL reference hardware, and there are no guarantee and no rights granted or executed of Panasonic's and or others' intellectual property rights and other rights regarding any technical information described in this document.

- Panasonic disclaims any and all liability for any losses, damages and infringement of any third partie's intellectual property rights and other rights incurred by AGL and/or any third parties arising from the use of these product date, figures, tables, or any and all information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Panasonic or others.

- 3. AGL has a rights to copy this document soleley for the purpose of use the AGL reference hardware, but any other rights (e.g., modification of this document) is subject to Panasonic's prior written consent. Notwithstanding the foregoing, Panasonic disclaims any and all liability for any losss, damages and infringement of any third partie's intellectual property rights and any other rights incurred by AGL or any third parties arising from the use of any copied and any modified documents.

- 4. AGL shall not used the products and technologies described in this document, directly or indirectly, for Military Purposes which is the design, development, manufacture, storage or use of any weapons, including, without limitation, nuclear weapons, chemical weapons, biological weapons and missiles. If any of the products or technical information described in this document is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- 5. All information such as product data, figures or tables described in this document is as of the released date of this document, and Panasonic may change the product and/or its specification without notice.

- 6. All information described in this doument has been carefully prepared with reasonable case, but any erorrs may be contained in this document. Panasonic shall not be liable for any losss, any damages incurred by AGL and/or any third parties arising from any error, bugs or faults of this document.

- 7. The products described in this document are intended to be used for general applications (such as entertainment, air conditioning, communications, measuring), and should not be used for Special Applications (such as for airplanes, aerospace, automotive driving equipment, traffic signaling equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body. It is to be understood that Panasonicshall not be held responsible for any damage incurred as a result of or in connection with your using the products described in this document for any Special Application.

- 8. Unless otherwise permitted by Panasonic or applicable Law, AGL shall not alter, modify, copy, or reverse engineer AGL Reference Hardware, whether in whole or in part.Panasonic disclaims any and all liability for any losses or damages incurred by AGL or third parties arising from such alteration, modification, copying or reverse engineering.

- 9. The product described in this document has a structure that can be easily disassembled, and there is a danger of accidents such as infants accidentally swallowing it by putting it in the mouth when any parts are removed from the product. Please take sufficient safety measures at your own risk to prevent such events from occurring. Panasonic is not liable for any accidents that occur due to such parts removed from the product by AGL.

- 10. The products desribed in this document is NOT designed to comply with any such as the environmental compatibility and Electro-Magnetic Compatibility of products. Panasonic is not liable for any damaged caused by your non-compliance with appliable laws or regulations.

- 11. AGL shall be resposible to cause any members of AGL to comply with any terms and condition described in this notice.

#### Regarding Software;

The provided patch files, yocto recipes and other files included in the AGL\_Refhw\_sample\_software\_yyyymmdd.tar.gz are

- (1) developed by Panasonic Corporation ("Panasonic"),

- (2) licensed under the GNU GENERAL PUBLIC LICENSE, Version 2 ("GPL"), and/or

- (3) open sourced software licensed under terms and conditions other than GPL.

We shall not be responsible or liable for any loss or damage that may occur due to the use of these files.